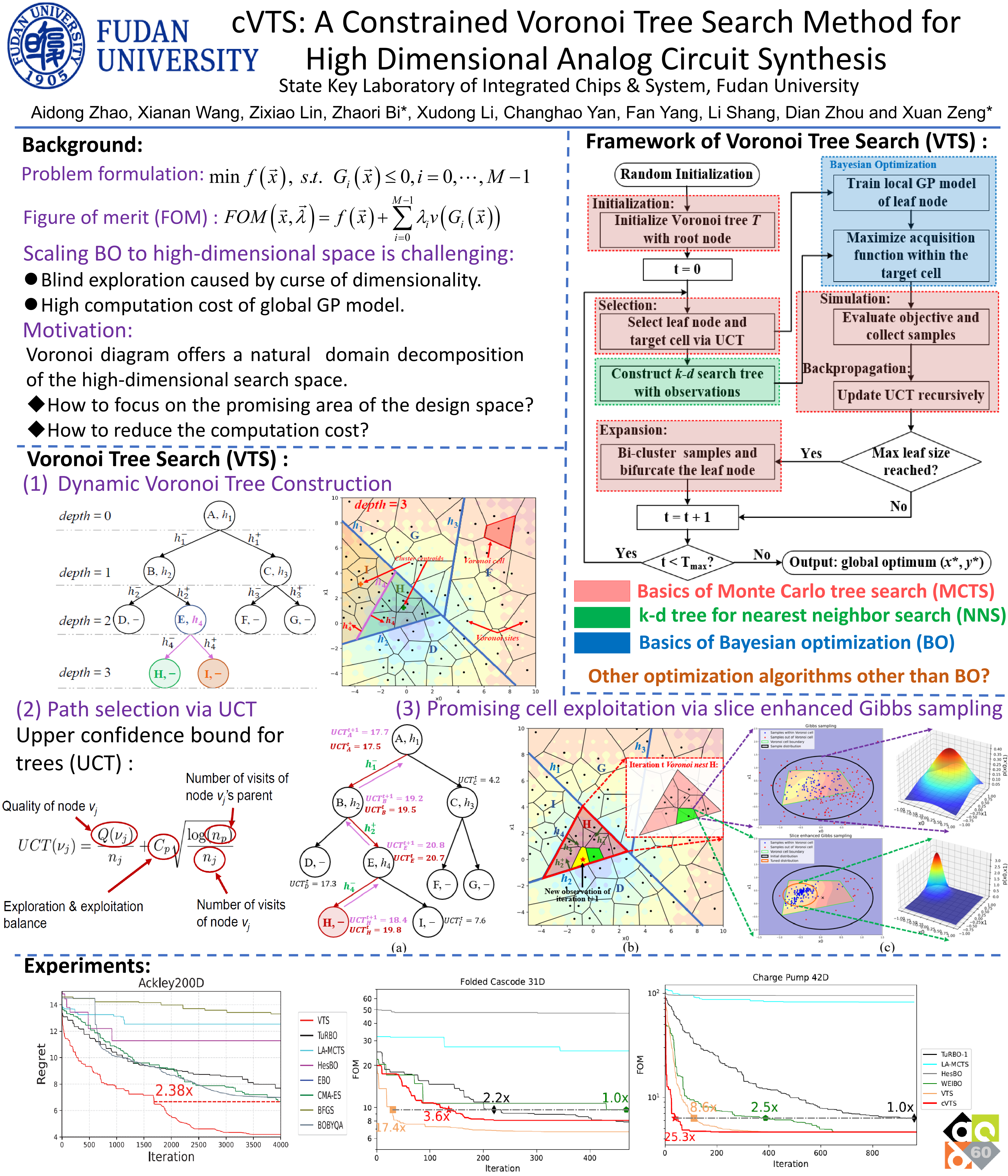

Our paper titled "cVTS A Constrained Voronoi Tree Search Method for High Dimensional Analog Circuit Synthesis" is accepted with 2023 60th DAC!

Abstract: A constrained Voronoi tree-based domain decomposition method for high dimensional Bayesian optimization is proposed to solve large scale analog circuit synthesis problems, which can be formulated as high-dimensional heterogeneous black-box optimization. Hierarchical Voronoi tree progressively breaks down the design space into partitions with implicit performance boundaries such that promising regions are efficiently explored. Fast exploitation is ensured in Voronoi nest via local Bayesian optimization with a few observations. A slice enhanced Gibbs sampling method is proposed to sample acquisition function cMES in irregular polyhedrons with design constraints. Compared with the state-of-the-art methods, cVTS achieved significant speed-up without loss of accuracy.